Architektúra počítačov je časť vedy o počítačoch, študujúca predovšetkým štruktúru, organizáciu, realizáciu a funkciu počítačov.

Za predpokladu, že počítač sa skladá z určitého počtu funkčných blokov, význam jednotlivých položiek môžeme spresniť takto:

štruktúra - popisuje prepojenie jednotlivých funkčných blokov

organizácia - popisuje dynamickú interakciu funkčných blokov a riadenie styku medzi nimi

realizácia - popisuje návrh a vnútornú štruktúru jednotlivých funkčných blokov

funkcia - popis chovania počítača ako celku navonok

Tieto štyri položky nám ukazujú cestu návrhu počítačov, pričom nie je možné jednotlivé úrovne návrhu od seba oddeľovať, nakoľko by sme tým prijímali značné obmedzenia.

Návrhár nových architektúr počítačových systémov sa musí opierať o tieto zdroje informácií:

1. Tradícia

2. Použiteľná technologická základňa

3. Vlastnosti živých organizmov

4. Fantázia

Začiatkom 40-tych rokov dvadsiateho storočia skupina vedcov pod vedením matematika maďarského pôvodu von Neumanna formulovala základné princípy architektúry počítačov platné dodnes:

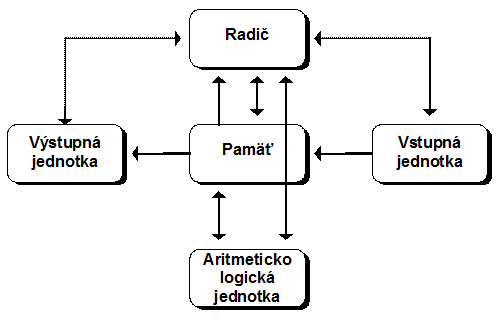

1. Počítač sa skladá z týchto funkčných jednotiek: pamäť, radič, aritmetická jednotka, vstupné a výstupné jednotky.

2. Štruktúra počítača je nezávislá na type riešenej úlohy, počítač sa programuje obsahom pamäti.

3. Inštrukcie a operandy sú v tej istej pamäti.

4. Pamäť je rozdelená do buniek rovnakej veľkosti, ich poradové čísla sa používajú ako adresy.

5. Program je tvorený postupnosťou príkazov - inštrukcií, v ktorých spravidla nie je obsiahnutá hodnota operandu, ale uvádza sa ich adresa, takže program sa pri zmene údajov nezmení. Inštrukcie sa vykonávajú jednotlivo v poradí, v ktorom sú zapísané do pamäti.

6. Zmena poradia vykonávania inštrukcií sa vyvolá inštrukciou podmieneného alebo nepodmieneného skoku.

7. Pre reprezentáciu inštrukcií a čísel sa používajú dvojkové signály a dvojková číselná sústava.

Podstatná časť von Neumannových myšlienok zostáva v platnosti dodnes a takmer vo všetkých sériovo vyrábaných počítačoch nájdeme uvedených sedem bodov.

Prvý počítač postavený na základe von Neumannovej koncepcie bol postavený v roku 1949 s názvom EDSAC.

CPU - je hlavnou činnou jednotkou, zabezpečujúcou predovšetkým riadiacu a synchronizačnú činnosť systému. Túto činnosť zabezpečuje radič a jeho podporné obvody, ktorý sa nachádza v každej CPU.

Každý ucelený systém, vykonávajúci definovanú činnosť potrebuje koordinačnú službu, ktorú zabezpečuje radič. Využíva k tomu vnútornú zbernicu pre internú komunikáciu a sadu interných pamäťových miest - registrov, ktoré môžu uchovávať medzivýsledky dôležité pre ďalšiu činnosť.

Veľmi dôležitou úlohou CPU je činnosť spojená s vyberaním a vykonávaním jednotlivých príkazov - inštrukcií. Každá inštrukcia je pre radič vlastne kódové slovo, na ktoré dekóder tohoto slova (dekóder inštrukcie) vyberie z vnútornej pevnej pamäte radiča postupnosť riadiacich a synchronizačných signálov. Tieto sú vnútornou zbernicou odoslané k ostatným výkonným jednotkám.

Ďalšou dôležitou úlohou radiča je správny výber ďalšej inštrukcie zo vstupnej postupnosti inštrukcií. Táto postupnosť býva najčastejšie uložená v operačnej pamäti a radič iba generuje ich jednotlivé adresy, pričom nie je ešte určené či sa jedná o inštrukčný kód alebo dátovú informáciu ako operandy.

Radič musí zaistiť správnu interpretáciu, čiže mikrokód implementovaný v radiči spätne ovplyvňovať.

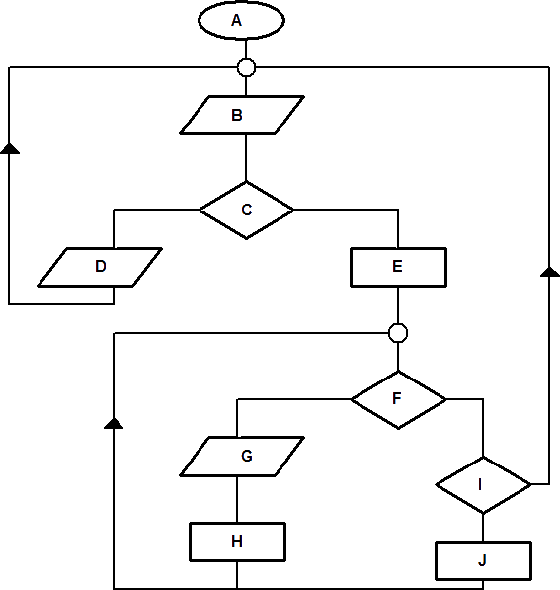

V prvej časti inštrukčného cyklu (A, B) radič prijme inštrukčný kód zo zbernice a vonkajšiemu prostrediu dá signál -"začínam vykonávať inštrukciu". Ďalej sa vykoná prvé dekódovanie inštrukčného kódu, ktoré určuje počet a typ ďalších dátových informácií nutných pre správne vykonanie načítanej informácie (C). Údaje môžu byť buď priamo prístupné alebo sa musia načítať z vonkajšieho zariadenia. V ďalšej časti inštrukčného cyklu sa vykonáva vlastná inštrukcia (E) definovaná inštrukčným kódom. Nasleduje časť, kedy CPU výsledky získané vykonaním operácie ukladá na zodpovedajúce miesta, ktoré sú definované v samotnom inštrukčnom cykle.

Posledná časť inštrukčného cyklu je kľudová a CPU čaká na vhodný okamžik, aby mohol začať s vykonávaním nového inštrukčného cyklu. Kontroluje stav vonkajšej zbernice a prijíma požiadavky na vykonanie neštandardných operácií alebo iba čaká (F, I).

Medzi neštandardné operácie patrí vykonávanie prázdnych inštrukčných cyklov (WAIT), uvoľnenie zbernice (HOLD) a vykonanie asynchronných procedúr (INTERRUPT ).

Cyklus WAIT je špeciálny cyklus CPU, kedy CPU čaká na dokončenie požadovanej operácie, ktorú vykonáva vonkajšie zariadenie k takej operácii prispôsobené.

Cyklus HOLD je špeciálny cyklus CPU, kedy CPU zachytila požiadavku na uvoľnenie riadenia vonkajšej zbernice. V prípade, že sa tak uskutoční, všetky obvody podieľajúce sa na riadení zbernice odpoja svoje vstupy a výstupy od zbernice a vyšlú správu - "zbernica odpojená". Po odpojení posledného riadiaceho obvodu, pridelí riadiaci obvod zbernicu tomu obvodu, ktorý túto situáciu vyvolal a vyšle správu, že zbernica je obsadená. Tento operáciu okamžite vykoná a po ukončení zbernicu uvoľní. Nadriadený obvod zbernice opäť prevezme riadenie a ak ju sám nepotrebuje, informuje sa či nemá o ňu nik záujem.

CPU za predpokladu, že počítač je konečný automat riadený sekvenciou príkazov a pracujúci s údajmi v binárnej forme, sa stará o súčinnosť mnohých takmer samostatných jednotiek. Každá takáto jednotka je na svoju činnosť optimalizovaná a pre komunikáciu využíva jasne definované protokoly. V ďalšom musí CPU zabezpečiť vykonávanie operácií daných algoritmom a tiež sa musí postarať o ukladanie informácií.

Rýchlosť CPU:

Mikroprocesor pracuje podľa určitého taktu hodín - frekvencia, ktorého správne nastavenie je dôležité pre jeho optimálnu činnosť. Pri malej frekvencii nie je dostatočne využívaná výkonnosť mikroprocesora a pri veľkej frekvencii neúmerne vzrastá počet chýb a tým sa zmenšuje výkonnosť. Frekvencia 1 MHz je milión taktov za sekundu. Staršie počítače PC XT používali hodiny s frekvenciou 6 MHz a vyššiu. Najnovšie typy procesorov využívajú to, že všetky externé zariadenia sú značne pomalšie ako vlastný procesor a ich interná frekvencia je niekoľkonásobne vyššia ako externá.

Šírka slova:

Šírka slova nám určuje, aké najväčšie číslo môže byť spracované v rámci jednej operácie. Býva 8, 16, 32 a 64 bitov. Samozrejme, ktorýkoľvek počítač môže byť naprogramovaný tak, aby spracovával ľubovoľne veľké číslo, musí však rozdeliť túto operáciu na rad podoperácii. Teda čím väčšia šírka slova, tým menej podoperácií a tým väčšia priechodnosť - výkonnosť.

Šírka prenosu údajov:

Šírka prenosu údajov určuje šírku, ktorou sú údaje presúvané do CPU. Môže byť 8, 16, 32 a 64 bitov. Šírka prenosu údajov nemusí byť zhodná so šírkou slova! Čím je väčšia šírka slova údajov ,tým je väčšia výkonnosť CPU. Napríklad príkaz MOV AX,0350 trvá pri procesore i8080 dvakrát dlhšie ako pri procesore i8086. Síce obidva majú rovnakú šírku slova, no majú rozdielnu šírku prenosu údajov (i8080 - 8 bitov, i8086 - 16 bitov).

Adresový priestor pamäte:

Adresový priestor pamäte stanovuje akú maximálne veľkú pamäť môže ten ktorý procesor využívať (adresovať). Opäť platí, čím väčší adresový priestor, ale samozrejme aj fyzická pamäť RAM, tým väčšia výkonnosť CPU. Najstaršie typy procesorov mohli adresovať len 64 kB, neskôr to bol 1 MB. Najnovšie typy procesorov umožňujú adresovať rádovo GB.

Mikroprocesor 8088:

Je použitý vo väčšine počítačov triedy PC XT. Je dodávaný v púzdre DIP (Dual In - line) so 40 vývodmi, čo je obdĺžnikové púzdro s dvoma radmi vývodov po 20. Klasický i8088 (označovaný tiež i8088-1) pracoval s frekvenciou do 5 MHz, neskôr bol vyvinutý i8088-2 (Turbo PC XT) s frekvenciou do 8 MHz. Procesor i8088 zodpovedá 29 000 tranzistorom.

Mikroprocesor 80286:

Navrhnutý firmou INTEL v roku 1981. Dodáva sa v púzdre PGA (Pin Grid Array), čo je mriežkové usporiadanie vývodov. Procesor i80286 zodpovedá 130 000 tranzistorom na pomerne malej ploche a preto je nutné chladenie formou doštičiek na jeho povrchu.

Mikroprocesor 80386:

Mikroprocesor i80386DX bol uvedený na trh v roku 1986 v puzdre PGA a zodpovedá 250 000 tranzitorom. Poskytuje omnoho širšie programovacie schopnosti ako i80286, umožňuje vykonávať aj programy v režime súbežného spracovania úloh. i80386SX sa líši od i80386DX tým, že SX má šírku prenosu len 16 bitov.

Mikroprocesor 80486:

Nepredstavoval taký výrazný skok ako napr. prechod z i80286 na i80386. V podstate môžeme povedať, že je to zmodernizovaná i80386. Jeho mikrokód je rozsiahlejší a rýchlejší. i80486 obsahuje v sebe okrem vylepšeného i80386 aj radič vyrovnávacej pamäte 80385 a numerický koprocesor 80387. 80486 zodpovedá 1,25 miliónu tranzistorov. Rozdiel medzi 80486DX a 80486SX spočíva v odpojení koprocesora pri 80486SX.

Postupom času sa začali dodávať na trh aj koprocesory, ktoré po pripojení k 486SX tento procesor úplne zatienili. Firma INTEL začala vyrábať čip nazývaný OVER DRIVE, ktorý sa zasúval do pätice pre 80487SX a pracoval s dvoma frekvenciami (internou a externou). Na princípe čipov OVER DRIVE sa začali vyrábať aj procesory s dvojitou frekvenciou označované DX2, prípadne so štvornásobnou frekvenciou DX4, čiže vnútorná frekvencia procesora bola dva, prípadne štyrikrát vyššia ako frekvencia, ktorou komunikoval s okolím.

| Výrobca | Typ | Max. rýchlosť(MHz) |

Šírka slova(b) |

Šírka prenosuúdajov (b) |

Operačná pamäť (MB) |

| INTEL | 8080 | 8 | 16 | 8 | 1 |

| INTEL | 8086 | 8 | 16 | 16 | 1 |

| INTEL | 8186 | 16 | 16 | 16 | 1 |

| NEC | V20 | 10 | 16 | 8 | 1 |

| NEC | V30 | 10 | 16 | 16 | 1 |

| INTEL | 80286 | 20 | 16 | 16 | 16 |

| INTEL | 80386D | 33 | 32 | 32 | 4096 |

| INTEL | 80386S | 20 | 32 | 16 | 16 |

| INTEL | 80486D | 33 | 32 | 32 | 4096 |

| INTEL | 80486S | 20 | 32 | 32 | 4096 |

Mikroprocesor PENTIUM:

Bol uvedený na trh len v nedávnej dobe a je plne kompatibilný s procesormi 80X86. Zodpovedá viac ako 3,1 miliónom tranzistorov. Jeho vnútorná architektúra je 32 bitová. Šírka prenosu údajov je 64 bitov. Optimálne výkony dosahuje pri frekvenciách 60 a 66 MHz. Jeho superskalárna architektúra umožňuje vykonávať viac ako 1 inštrukciu počas jedného taktu.

Hlavné odlišnosti od predchádzajúcich procesorov, ktoré umožnili zväčšiť jeho výkonnosť:

• superskalárna architektúra

• oddelená kódová a dátová vyrovnávacia pamäť (CACHE)

• predikcia vetvenia inštrukcií

• vylepšená 64 bitová dátová zbernica

• voľba veľkostí stránky pamäte

• monitorovanie výkonu

• detekcia chýb a funkčná redundancia

Superskalárna architektúra:

Schopnosť vykonávať viac inštrukcií v jednom takte, je umožnená dvoma kanálmi, ktoré môžu spracovávať 2 inštrukcie súčasne, čo umožňuje existencia dvoch aritmeticko-logických jednotiek.

Typy údajov:

Elementárnou jednotkou množstva informácií je jeden bit (b). Najmenšou adresovateľnou jednotkou, t.j. najmenšie množstvo informácií, ktoré sa ukladá do pamäte je 1 Byt = 8 bitov, niekedy označovaný aj ako slabika.

Bit najnižšieho rádu sa označuje nulou (LSB).

Bit najvyššieho rádu sa označuje sedmičkou (MSB).

Všetky ostatné jednotky, ktoré využíva procesor sú odvodené od slabiky:

Spojenie dvoch slabík sa nazýva slovo (WORD - používaná skratka W). Bity slova sú číslované 0-15, bity 0-7 tvoria dolnú slabiku, bity 8-15 tvoria hornú slabiku

| horná slabika | dolná slabika |

4 slabiky vytvárajú dvojslovo - označujeme ho DOUBLE.

8 slabík vytvára štvorslovo - označujeme ho QUARD.

Adresy slov nemusia byť zarovnané na párne adresy (adresa slova nemusí byť deliteľná dvoma).

Organizácia pamäte:

Pamäť pripojená na zbernicu procesora sa nazýva fyzická pamäť. Je organizovaná ako postupnosť slabík, pričom každej je priradená fyzická adresa, ktorá je v intervale 0-232-1 (4GB).

Používateľ (programátor) však využíva virtuálnu pamäť. Prechod medzi fyzickými adresami a virtuálnou pamäťou zabezpečuje správa pamäti, ktorá ponúka užívateľovi segmentovanie a stránkovanie.

Segmentovanie je mechanizmus poskytujúci násobný a nezávislý prístup k adresovému priestoru.

Stránkovanie pamäti podporuje vytváranie rozsiahlejšieho adresového priestoru, než je kapacita fyzickej pamäti s použitím vonkajšej diskovej pamäte.

Môžu sa používať obidva mechanizmy alebo len jeden.

Ak sa program odkazuje na pamäť, použije logickú adresu. Táto sa segmentovaním predkladá sa nesegmentovanú lineárnu adresu. Stránkovanie následne lineárnu adresu prekladá na fyzickú, ak však nie je zapnuté stránkovanie, lineárna adresa sa rovná fyzickej.

Segmenty využívané segmentáciou sú vzájomne nezávislé priestory pamäte. Rôzne segmenty sa vytvárajú pre inštrukcie privádzané do programu, rôzne pre údaje alebo zásobník. Jeden proces môže mať až 16 383 segmentov rôznych veľkostí a typov. Logická adresa sa skladá zo selektoru a offsetu. Selektor nás informuje okrem iného o báze (adresa začiatku) segmentu a veľkosti segmentu.

OFFSET - je relatívna adresa vo vnútri segmentu a počíta sa od jeho začiatku, samozrejme nesmie prekročiť veľkosť segmentu.

Logickú adresu zapisujeme v tvare: selektor: offset

Výhodou segmentácie je, že sa kontrolujú prístupy k jednotlivým segmentom, kontroluje sa prekročenie veľkosti, oprávnenie prístupu k segmentu a typ operácie vykonávaný so segmentom.

Registre:

Mikroprocesory radu 80X86 a Pentium využíva tieto 3 skupiny registrov:

• všeobecné registre - osem 32-bitových registrov, ktoré môže väčšinou voľne používať programátor

• segmentované registre - šesť 16-bitových registrov, určených pre uloženie selektoru

• príznakový register EFLAGS a register smerníka inštrukcie (EIP)

Všeobecné registre:

Patria sem EAX, EBX, ECX, EDX, ESI, EDI, EBP, ESP

Do všetkých týchto registrov sa dajú ukladať výsledky a operandy pre aritmetické a logické operácie. Tiež je možné ich použiť pre adresové výpočty okrem registra ESP.

Je možné zvlášť používať dolné slovo registrov AX, BX, CX, DX a aj ich horné aj dolné slabiky AH, BH,CH, DH, AL,BL, CL, DL.

Mená registrov majú svoj význam:

• EAX - akumulátor

• EBX - bázový register často sa používa ako offsetová časť adresy

• ECX - čítač (inštrukčné cykly)

• EDX - všeobecný údajový register

• ESI, EDI, EBP, ESP sa najčastejšie používajú pre uloženie offsetovej časti adresy

• ESP - obsahuje offset adresy vrcholu zásobníka

• EBP - je určený prevažne pre uloženie offsetovej časti adresy zásobníka

• ESI - EDI indexové registre

• ESI - indexové registre pre uloženie offsetovej adresy zdrojového operanda

• EDI - indexové registre pre uloženie offsetovej adresy cieľového operanda

Tieto konvencie je nutné dodržiavať pri práci s reťazcami. Zostavenie registra ESP je výsadné a nemenné. Procesory vyrábané pred i80386 mali iba 16 a 8 bitové časti registrov.

Segmentové registre:

Je to šesť 16-bitových registrov slúžiacich pre uloženie selektora segmentu.

Patria sem:

• CS (code segment) v spojení s EIP je určený pre adresáciu kódu (inštrukcie), adresovanie inštrukčných segmentov

• DS (data segment) v spojení so všeobecným registrom adresuje údaje. Ako pomocné dátové registre sa používajú ES(extra), FS a GS

• SS (stack segment) zásobníkový , slúži na určenie vrcholu zásobníka v spojení s registrom ESP a EBP

Registre FS a GS používajú až procesory počínajúc typom i80386. Veľkosť všetkých segmentových registrov zostáva u všetkých typoch procesorov rovnaká.

Príznakový register:

Obsahuje dve skupiny príznakových registrov. Prvá skupina sú príznaky nastavované procesorom. Druhá skupina sú príznaky nastavované používateľom, pomocou ktorých môže čiastočne riadiť chod procesora (napr. príznak PF - kontrola parity, DF - smer vykonávania,...).

EIP - register smerníka inštrukcie obsahuje vždy offsetovú časť práve vykonávanej inštrukie. Používateľ nemá možnosť meniť priamo obsah tohto registra.

Príkazy určené procesoru na spracovanie sa zadávajú vo forme inštrukcií, ktoré sa skladajú z dvoch častí:

a) operačný znak je vlastným príkazom pre procesor

b) operandy obsahujú vlastné údaje

Spôsob sprístupnenia - adresovania operandov sa uskutočňuje nasledovnými technikami.

Operand je priamo uložený v niektorom 32-bitovom (prípadne 16 alebo 8 bitovom) všeobecnom registri. Môžu sa taktiež využívať registrové páry, ktoré vznikajú spojením dvoch registrov.

Príklad: MOV AX, CX (Prepíš obsah registra CX do AX)

Operand je priamo uložený v inštrukcii ako konštanta.

Príklad: MOV AX, 120 (Naplň register AX hodnotou 120)

Týmto spôsobom sa sprístupňujú operandy uložené vo fyzickej pamäti. Každá adresa sa získava zložením segmentu (príp. selektoru) a offsetu.

Segmentový register sa určuje väčšinou implicitne. Implicitná voľba je daná niekoľkými faktormi, ako hlavný je typ operácie s pamäťovým registrom. Podľa typu spracovávaného operandu sa potom vyberá segmentový register, ktorý sa použije pre výpočet lineárnej adresy operandu.

| Prístup k | Použitý register | Operácia |

|---|---|---|

| inštrukciám | CS (Code Segment) | Výber operačného znaku alebo priameho operandu |

| zásobníkom | SS (Stack Segment) | Pri všetkých prístupoch k zásobníku v spojitosti s registrom ESP alebo EBP |

| údajom | DS (Data Segment) | Pri všetkých prístupoch k údajom v pamäti okrem zásobníka a priamych operandov. V reťazcových operáciách pre segmentovanie zdrojového operandu |

| alternatívnym údajom |

ES (Extra Segment) | V reťazcových operáciách pre segmentovanie cieľového operandu |

V prípade potreby je možné pre jednu inštrukciu pomocou prefixu zmeniť implicitné priradenie segmentového registra. Prefixami nie je možné zmeniť nastavenie segmentového registra v týchto prípadoch:

- cieľový reťazec v reťazcových operáciách je vždy segmentovaný registrom ES

- operácia uloženia do zásobníka a výberu zo zásobníka sa vždy segmentuje registrom SS

- výber inštrukcií sa vždy segmentuje registrom CS

Offsetová časť adresy je uložená v niektorom zo všeobecných registrov

Príklad:

MOV BH, CS: [AX] (Nepriama adresa)

MOV AH, GS: Adresa

MOV BH, CS: [AX] (Nepriama adresa CS : AX a implicitne si vyberá dátový segment)

MOV AH, CS: Adresa (Priama adresa cez GS)

Vstupné a výstupné operácie vykonávajú procesory 80x86 prostredníctvom V/V brán (I/0 - ports). Vstupno výstupné brány sú registre v radičoch periférnych zariadení. Vstupno výstupná brána môže byť vstupná, výstupná alebo obojsmerná a z toho vyplýva, že z nej môžeme iba čítať, iba zapisovať, alebo aj čítať aj zapisovať.

Vstupno výstupné brány môžeme adresovať dvoma spôsobmi:

1. Prostredníctvom zvláštneho adresového priestoru a V/V inštrukcií.

2. Mapovanie V/V brán do adresového priestoru fyzickej pamäte.

1. Adresovanie pomocou zvláštneho adresového priestoru

CPU pre adresáciu V/V brán poskytne oddelený 16-bitový adresový priestor, teda môžeme samostatne adresovať 64 kB V/V brán. Brány sú 8-bitové a je možné ich spájať do 16-tich prípadne 32 bitov.

Pre prístup k V/V bránam nám slúžia inštrukcie IN, OUT, ktoré prenášajú údaje medzi akumulátorom a V/V bránou.

To, či adresa nastavená na adresovej zbernici sa použije na prístup do pamäte alebo do vstupno-výstupného adresového priestoru indikuje signál M/IO (Memory Input Output).

2. Mapovanie V/V brán do adresového priestoru fyzickej pamäte

V tomto prípade adresujeme vstupno-výstupné brány priamo do adresového priestoru fyzickej pamäte. Výhodou takéhoto usporiadania je, že pre ovládanie V/V brán je možné použiť všetky inštrukcie pre prácu s pamäťou a všetky dostupné adresovacie techniky. Dôležité je zabezpečiť synchronizáciu V/V operácií, aby napr. čítanie V/V brány nepredbiehalo zápis do nej.

V súčasnej dobe využívajú procesory na báze 80x86 tieto druhy primárnych pamätí:

1. konvenčná,

2. rozšírená EXTENDED - XMS,

3. prekrývaná, stránkovaná EXPANDED - EMS.

Konvenčná pamäť

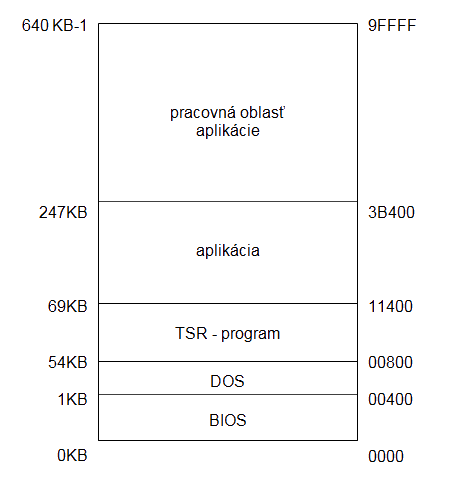

80x86 pri svojej činnosti pod operačným systémom MS DOS využíva prvých 640 kB, ktorých využitie je následujúce:

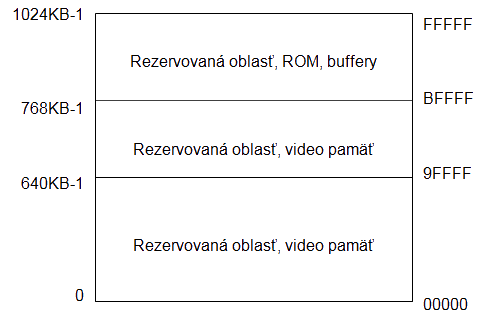

Adresový priestor nad 640 kB, ktorý je schopný adresovať aj 8088 a 8086 sa využíva nasledovne:

Extended Memory - XMS

Procesory od 80286 sú schopné adresovať väčší adresový priestor než 1MB. Aby však mohli využívať túto pamäť nad 1 MB musia sa prepnúť do tzv. chráneného režimu (protected mode), ktorý nie je kompatibilný s reálnym režimom procesorov 8088, 8086.

Chránený režim vymedzí každej aplikácii určitý pamäťový priestor a v prípade, že sú prekročené jeho hranice, je aplikácia ukončená. Aby mohla byť využívaná rozšírená pamäť, musí byť k tomu aplikácia špeciálne naprogramovaná.

Expanded Memory - EMS

Väčšina DOS aplikácií však nevie využívať XMS. Preto firmy LOTUS, INTEL, MICROSOFT vyvinuli štandard pre programový produkt, ktorý prekračuje obmedzenie DOSu pomocou stránkovania. V rezervovanej pamäti (640-1024 kB) sa alokuje 64kB pre 4 stránky (1 stránka - 16 kB).

V počítačoch 80386 a vyšších je nutné pre EMS používať program EMM386.